Erro de Hardware do Protótipo do Circuito de Amostragem de Bateria

Jan 23, 2025

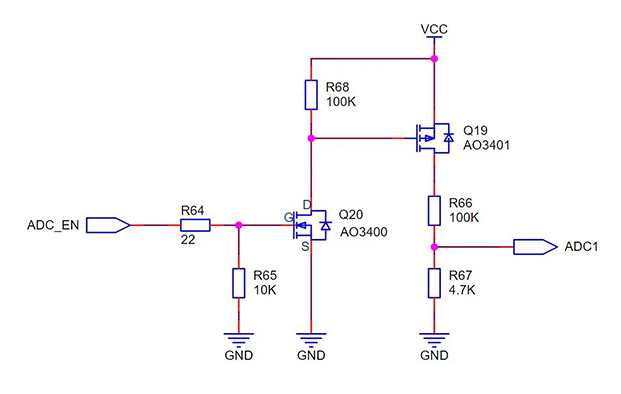

Como diz o ditado, 'Está tudo bem se o circuito e eu conseguirmos funcionar. Se o circuito não funcionar, eu funcionarei.' A edição de hoje traz um bug de hardware de um membro do grupo. Sem mais delongas, vamos dar uma olhada: Descrição do problema: A amostragem da bateria do produto protótipo de circuito tem uma probabilidade de 40uA de corrente de fuga adicional. Um dos cinco protótipos apresenta esse fenômeno anômalo. O problema está localizado no PMOS, e substituir o PMOS é útil. O esquema do circuito é o seguinte:

Quando ADC_EN está alto, o tubo NMOS Q20 é ativado, o tubo PMOS Q19 é ativado e o ADC1 coleta a tensão de VIN (ADC1≈VCC*4.7K/104.7K). Quando ADC_EN está baixo, tanto o NMOS quanto o PMOS são desligados, e não haverá corrente de fuga em R66 e R67 (circuito necessário para baixo consumo de energia).

De acordo com o diagrama esquemático, não há problema, mas a anomalia real é que quando o Q19 está desligado, ainda há uma corrente de fuga de 40uA. Análise da causa: Após verificar cuidadosamente a tensão VIN com amigos do grupo, foi descoberto que a tensão da bateria correspondente ao VIN é uma bateria de 12V, ou seja, a tensão da bateria será maior (superior a 12V) após estar totalmente carregada. E este diagrama esquemático foi copiado do circuito de coleta de bateria de lítio de 4.2V.

Quando o NMOS está ligado, a tensão VGS em ambas as extremidades do PMOS é quase igual a VIN (maior que 12V), e o PMOS utilizado é o AO3401, e sua tensão de suporte VGS máxima absoluta é de ±12V. Além disso, o problema será resolvido após a substituição do PMOS conforme descrito acima, portanto, suspeita-se que a sobretensão VGS do PMOS cause danos internos ao PMOS, o que pode gerar corrente de fuga adicional.

Postagens Recentes

26 de outubro de 2016

O Contratante de Engenharia Mais Bem-sucedido

May 06, 2025

Processo de Design de PCB e Pontos Chave